# UNISONIC TECHNOLOGIES CO., LTD

US2651 Preliminary CMOS IC

# HIGH PRECISION LOW COST MCM POWER SWITCH

#### **■ DESCRIPTION**

The UTC **US2651** is a high performance, high precision and low cost PWM Power switch for non-isolated buck application. It combines a dedicated current mode PWM controller and error amplifier for low component count. UTC **US2651** use UTC proprietary frequency shuffling technique for EMI performance. And oscillator with frequency-reduction control is implemented.

The UTC **US2651** has soft start control and protection function, such as Cycle-by-Cycle current limiting, Over Loading Protection, Output Short-Circuit Protection,  $R_{CS}$  short Protection, OTP,  $V_{DD}$  OVP, and UVLO.

#### ■ FEATURES

- \* Power on soft-start

- \* Load compensation

- \* Built-in error amplifier

- \* Oscillator of fixed frequency with frequency-reduction control

- \* Frequency shuffling for EMI improvement

- \* Built-in Leading Edge Blanking (LEB)

- \* Cycle-by-Cycle current limiting

- \* Over loading protection

- \* Output short-circuit protection

- \* V<sub>DD</sub> Under Voltage Lockout with hysteresis (UVLO)

- \* V<sub>DD</sub> OVP

# ORDERING INFORMATION

| Ordering      | Number        | Deelsone | Packing   |  |

|---------------|---------------|----------|-----------|--|

| Lead Free     | Halogen Free  | Package  |           |  |

| US2651L-D08-T | US2651G-D08-T | DIP-8    | Tube      |  |

| US2651L-S08-R | US2651G-S08-R | SOP-8    | Tape Reel |  |

<u>www.unisonic.com.tw</u> 1 of 6

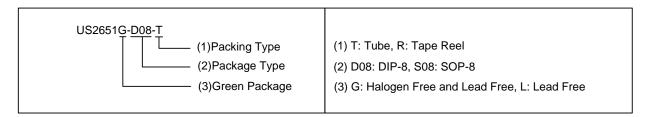

#### ■ MARKING

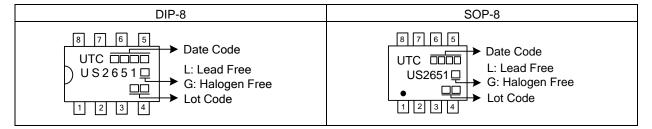

#### **■ PIN CONFIGURATION**

# ■ PIN DESCRIPTION

| -       | 1        |                                                                                                     |  |  |  |

|---------|----------|-----------------------------------------------------------------------------------------------------|--|--|--|

| PIN NO. | PIN NAME | DESCRIPTION                                                                                         |  |  |  |

| 1       | $V_{DD}$ | Power supply                                                                                        |  |  |  |

| 2       | COMP     | Loop compensation for CV stability                                                                  |  |  |  |

| 3       | NC       | Not connected                                                                                       |  |  |  |

| 4       | CS       | Current sense input                                                                                 |  |  |  |

| 5, 6    | DRAIN    | HV MOSFET Drain Pin. The Drain pin is connected to the primary lead of the transformer/ inductance. |  |  |  |

| 7, 8    | GND      | Ground                                                                                              |  |  |  |

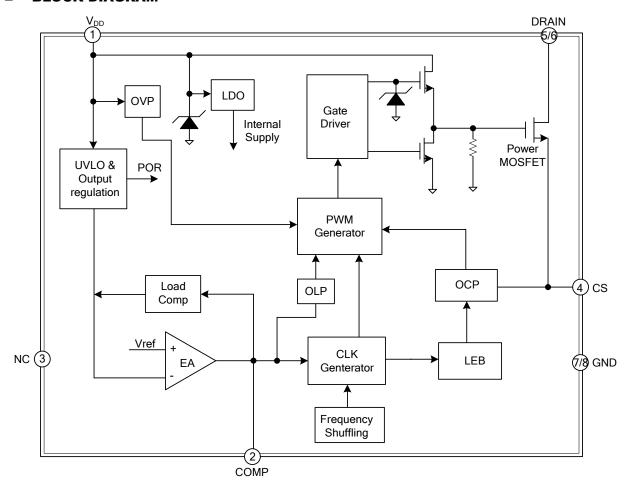

# **■ BLOCK DIAGRAM**

# ■ ABSOLUTE MAXIMUM RATING

| PARAMETER                                       | SYMBOL            | RATINGS            | UNIT |

|-------------------------------------------------|-------------------|--------------------|------|

| Drain Voltage (Off State)                       | B <sub>VDSS</sub> | -0.3 ~ BVdss       | V    |

| V <sub>DD</sub> Voltage                         |                   | -0.3 ~ 40          | V    |

| V <sub>DD</sub> Zenzer Clamp Continuous Current | I <sub>DD</sub>   | 10                 | mA   |

| COMP Voltage                                    | $V_{COMP}$        | -0.3 ~ 7           | V    |

| CS Input Voltage                                | V <sub>CS</sub>   | -0.3 ~ 7           | V    |

| Operating Junction Temperature                  | $T_J$             | -40 ~ <b>+</b> 150 | °C   |

| Storage Temperature                             | T <sub>STG</sub>  | -55 ~ <b>+</b> 150 | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

# **■ THERMAL DATA**

| PARAMETER           |       | SYMBOL        | RATINGS | UNIT |

|---------------------|-------|---------------|---------|------|

| Lunction to Ambient | DIP-8 | $\theta_{JA}$ | 75      | °C/W |

| Junction to Ambient | SOP-8 |               | 90      | °C/W |

# ■ **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub>=25°C, V<sub>DD</sub>=16V, if not otherwise noted)

| PARAMETER                                                        | SYMBOL                 | TEST CONDITIONS                                         | MIN | TYP  | MAX | UNIT |

|------------------------------------------------------------------|------------------------|---------------------------------------------------------|-----|------|-----|------|

| SUPPLY VOLTAGE (VDD) SECTION                                     |                        |                                                         |     |      |     |      |

| Standby Current                                                  | I <sub>DD ST</sub>     | V <sub>DD</sub> = U <sub>VLO (OFF)</sub> -0.1V          |     |      | 35  | μA   |

| Operation Current                                                | I <sub>DD OP</sub>     | Operation Supply Current CS=0V, V <sub>DD</sub> =18V    |     |      | 3.0 | mA   |

| V <sub>DD</sub> Under Voltage Lockout Enter                      | $U_{VLO(ON)}$          | V <sub>DD</sub> Falling                                 |     | 8.5  | 10  | V    |

| V <sub>DD</sub> Under Voltage Lockout Exit                       | U <sub>VLO (OFF)</sub> | V <sub>DD</sub> Rising                                  | 13  | 14.5 | 16  | V    |

| Over Voltage Protection Threshold                                | OVP                    | Ramp V <sub>DD</sub> Until Gate Shut Down               | 26  | 27.5 | 29  | V    |

| In Normal Regulation, V <sub>DD</sub> will be Regulated to 19.3V | $V_{DD}$               | Ramp V <sub>DD</sub> Until Comp Voltage Lower than 2.5V | 17  | 18.5 | 20  | V    |

| <b>CURRENT SENSE INPUT SECTION</b>                               | ON                     |                                                         | •   | •    |     |      |

| LEB Time                                                         | T <sub>LEB</sub>       |                                                         |     | 300  |     | ns   |

| Over Current Threshold                                           | $V_{TH\_OC}$           |                                                         | 750 | 860  | 990 | mV   |

| OCP Propagation Delay                                            | $T_{D\_OC}$            |                                                         |     | 110  |     | ns   |

| Input Impedance                                                  | Z <sub>SENSE_IN</sub>  |                                                         | 40  |      |     | ΚΩ   |

| FREQUENCY SECTION                                                |                        |                                                         |     |      |     |      |

| IC Maximum Frequency                                             | F <sub>req_MAX</sub>   |                                                         | 40  | 50   | 60  | KHz  |

| Frequency Shuffling Range                                        | ∆ f/F <sub>req</sub>   |                                                         |     | ±6   |     | %    |

| ERROR AMPLIFIER SECTION                                          |                        |                                                         |     |      |     |      |

| DC Gain of EA                                                    | Gain                   |                                                         |     | 60   |     | dB   |

| Max. Cable Compensation Current                                  | I_COMP_MAX             | V <sub>DD</sub> =18V, C <sub>OMP</sub> =0V              |     | 6    |     | μΑ   |

| POWER MOSFET SECTION                                             |                        |                                                         |     |      |     |      |

| MOSFET Drain-Source<br>Breakdown Voltage                         | BV <sub>DSS</sub>      |                                                         | 600 |      |     | V    |

| On Resistance                                                    | R <sub>DS(ON)</sub>    | tatic, I <sub>D</sub> =0.45A                            |     | 15   |     | Ω    |

#### **■ OPERATION DESCRIPTION**

The UTC **US2651** is a cost effective PWM power switch optimized for off-line non-isolated buck applications including electrical appliance and linear regulator replacement. It operates in current mode and regulates output voltage with dedicated features. High integration can afford low cost and component count solution.

#### Startup Current and Start up Control

Startup current of UTC **US2651** is designed to be very low so that V<sub>DD</sub> could be charged up above UVLO threshold and starts up quickly. A large value startup resistor can therefore be used to minimize the power loss in application.

#### **Operating Current**

The Operating current of UTC **US2651** is as low as 3mA. Good efficiency is achieved with the low operating current together with 'Muti-mode' control features.

#### Oscillator operationF

The switching frequency of UTC **US2651** is internally fixed at 50KHz. No external frequency setting components are required for PCB design simplification.

At light load or zero load condition, most of the power dissipation in a switching mode power supply is from switching loss on the MOSFET. The magnitude of power loss is in proportion to the switching frequency. Lower switching frequency leads to the reduction on the power loss and thus conserves the energy. The switching frequency is internally adjusted at light load or no load condition. The switch frequency reduces at light/no load condition to improve the conversion efficiency. The minimum switching frequency is 400Hz.

#### Frequency shuffling for EMI improvement

The frequency shuffling (switching frequency modulation) is implemented in UTC **US2651**. The oscillation frequency is modulated so that the tone energy is spread out. The spread spectrum minimizes the conduction band EMI and therefore eases the system design.

#### **Built-in error amplifier**

In UTC **US2651**, on-chip EA (error amplifier) is implemented to regulate output voltage. Through inner resistor divider, the V<sub>DD</sub> voltage is detected at inverter input of EA to regulate output voltage.

#### Load Compensation for good CV regulation

In UTC **US2651**, load compensation is implemented to achieve good load regulation. An offset voltage is generated at inverter input of EA by an internal current flowing into the resister divider. The current is inversely proportional to the voltage across pin COMP, as a result, it is inversely proportional to the output load current, thus the output voltage can be compensated specially in zero loading condition. As the load current decreases from full-load to no-load, the offset voltage at inverter input of EA will increase.

#### **Current Sensing and Leading Edge Blanking**

Cycle-by-Cycle current limiting is offered in UTC **US2651** current mode PWM control. The switch current is detected by a sense resistor into the CS pin. An internal leading edge blanking circuit chops off the sensed voltage spike at initial internal power MOSFET on state so that the external RC filtering on sense input is no longer needed. The PWM duty cycle is determined by the current sense input voltage and the EA output voltage.

#### Gate Drive

The internal power MOSFET in UTC **US2651** is driven by a dedicated gate driver for power switch control. Too weak the gate drive strength results in higher conduction and switch loss of MOSFET while too strong gate drive compromises EMI.

A good tradeoff is achieved through the built-in totem pole gate design with right output strength control.

# **Protection Control**

Good power supply system reliability is achieved with its rich protection features including Cycle-by Cycle current limiting (OCP), Over Loading Protection, Over Voltage Protection, Output Short-Circuit Protection and Under Voltage Lockout on V<sub>DD</sub> (UVLO).

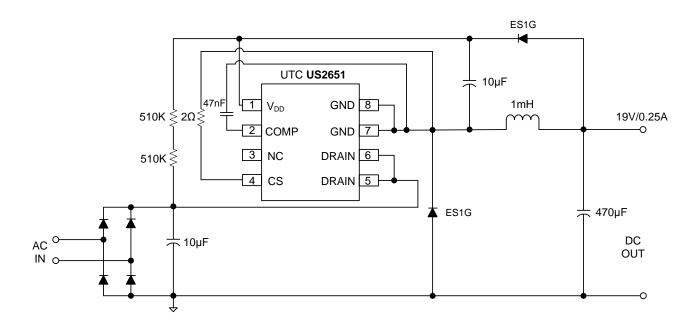

#### TYPICAL APPLICATION CIRCUIT

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.